在智能汽车、工业控制、5G通信等高可靠性要求的领域,一颗芯片的失效可能引发系统级故障,甚至危及人身安全。如何确保芯片在真实使用环境中长期稳定运行?芯片板级可靠性测试(Board Level Reliability, BLR)正是这一问题的关键答案。通过模拟极端温度变化、剧烈振动、冲击等应力环境,BLR能在产品量产前精准识别焊点疲劳、材料分层、电气开路等潜在失效风险,大幅降低现场失效率——研究表明,完善的BLR方案可减少80%以上的早期失效问题。

什么是BLR测试?

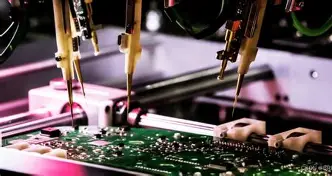

BLR测试聚焦于已贴装在PCB上的元器件(如BGA、CSP、SOP等封装形式),评估其在模拟实际使用环境下的结构与电气可靠性。它不仅是AEC-Q100等车规认证的强制环节,更是高端工业与消费电子品质升级的核心手段。

核心测试项目与失效机制

BLR测试覆盖温度与机械两大环境应力,每项均对应明确的失效模式:

温度环境试验

| 测试项目 | 参考标准 | 主要失效机制 |

|---|---|---|

| 温度循环 | JESD22-A104, EIAJ ED-4701-100, IPC 9701 | 热疲劳断裂、蠕变疲劳断裂 |

| 冷热冲击 | JESD22-A106, EIAJ ED-4701B-141 | 焊点脆裂、界面分层 |

机械环境试验

| 测试项目 | 参考标准 | 主要失效机制 |

|---|---|---|

| 机械冲击 | JESD22-B110, JESD22-B111A | 静态断裂、振动断裂、蠕变断裂 |

| 机械振动 | JESD22-B103B | 焊点微裂、引脚松动 |

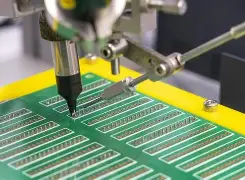

| PCB弯曲试验 | IPC 9702, JESD22-B113A | 基板分层、内层线路断裂 |

监控链路等级:从芯片到PCB的全路径追踪

BLR测试通过四级监控链路设计,实现从芯片内部到PCB外层的失效定位:

- Level 0:布线深入芯片内部(与晶圆制程相关)

- Level 1:连接芯片表面金属层,监测内部焊点

- Level 2:延伸至基板内层,检测应力导致的内层断裂或分层

- Level 3:通过基板表面布线连接PCB,观察焊点与PCB界面异常

该分级机制极大提升了失效分析的精准度,为设计优化提供直接依据。

实验后关键检查手段

BLR测试后,需通过多维度分析确认失效位置与模式:

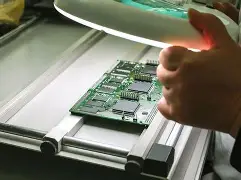

- ✅ 金相切片:对特定焊球或引脚进行截面分析,观察微观裂纹与界面状态

- ✅ 红墨水拉拔测试:针对BGA全阵列焊球,快速定位断裂界面(如焊盘 lifted pad)

- ✅ 电气连通性检测:实时监控开路、短路等电性能异常,关联物理失效

为什么选择专业BLR服务?

- 标准全覆盖:支持JEDEC、IPC、AEC-Q等国际主流标准

- 场景全覆盖:温度循环、冷热冲击、机械振动、跌落冲击等真实工况模拟

- 分析全链条:从应力测试到失效分析(FA),提供根因诊断与改进建议

- 资质有保障:CNAS/CMA认证实验室,获多家头部终端客户认可

- 响应更高效:全国多实验室布局,缩短交付周期

总结

芯片板级可靠性测试(BLR)绝非简单的“过流程”,而是产品可靠性的核心防线。在电子设备日益小型化、高集成化的趋势下,焊点与封装结构承受的应力愈发复杂。唯有通过系统化、标准化的BLR验证,才能确保产品在严苛环境中“扛得住、用得久”。无论是进军汽车电子,还是提升工业设备寿命,BLR都是不可绕行的技术门槛。

深圳德恺检测专注于半导体与电子元器件可靠性测试,具备CNAS/CMA双重资质,服务覆盖BLR、PCBA可靠性评估、锡须检查、离子清洁度分析等全链条项目。我们依托国际先进设备与资深FA团队,为客户提供从测试到失效分析的一站式解决方案,助力产品高效通过AEC-Q、JEDEC等严苛认证。