在全球“双碳”目标与绿色电子趋势推动下,低功耗已成为半导体设计的关键指标。无论是物联网终端、可穿戴设备,还是AI边缘计算芯片,功耗控制直接决定产品续航、发热与用户体验。然而,如何精准测试并验证芯片的真实能效,仍是行业普遍面临的挑战。本文将系统梳理低功耗芯片的关键测试方法与能效验证技术,为研发与验证提供实用参考。

为什么低功耗测试如此复杂?

功耗的“多维面孔”

低功耗芯片的功耗表现并非单一数值,而是由多个维度构成:

- 静态功耗(Static Power):晶体管漏电流导致的待机功耗

- 动态功耗(Dynamic Power):开关活动引起的瞬时功耗

- 瞬态功耗(Transient Power):状态切换时的尖峰电流

- 工作模式功耗:如睡眠、唤醒、高性能等不同状态下的能耗差异

这些维度相互交织,使得测试必须覆盖全场景、全电压、全温度范围。

核心测试方法一览

1. 静态功耗测试

- 测试目标:测量芯片在无时钟、无信号切换时的漏电流

- 关键设备:高精度源表(SMU)、皮安计

- 测试要点:需在高温(如125°C)下进行,以暴露漏电最严重工况

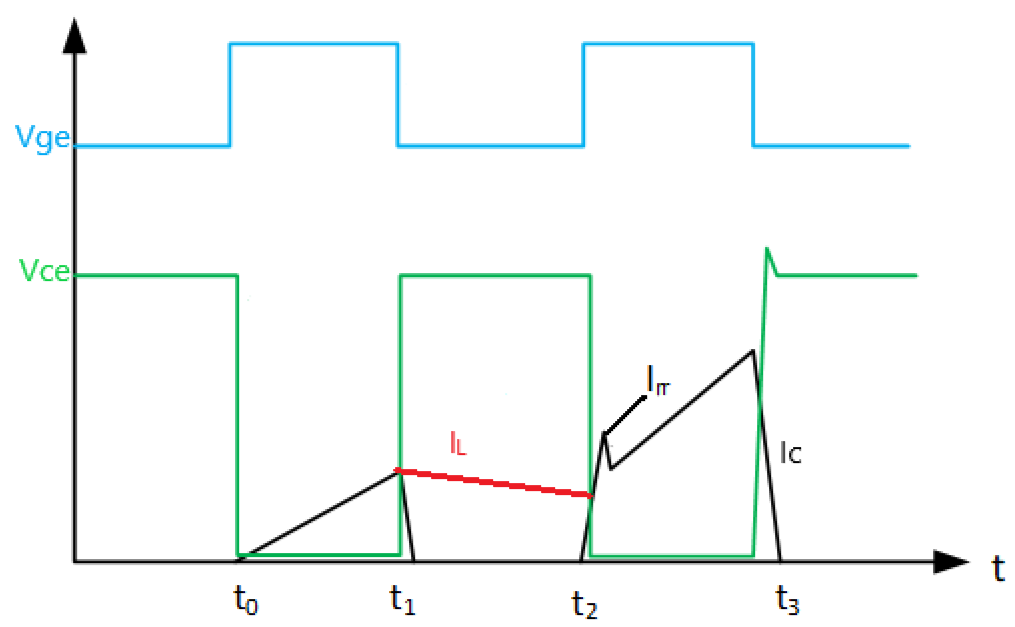

2. 动态功耗测试

- 激励方式:施加典型工作负载(如Dhrystone、CoreMark)

- 测量手段:高速电流探头 + 示波器,或集成式电源分析仪

- 输出指标:平均功耗、峰值功耗、能效比(如 DMIPS/mW)

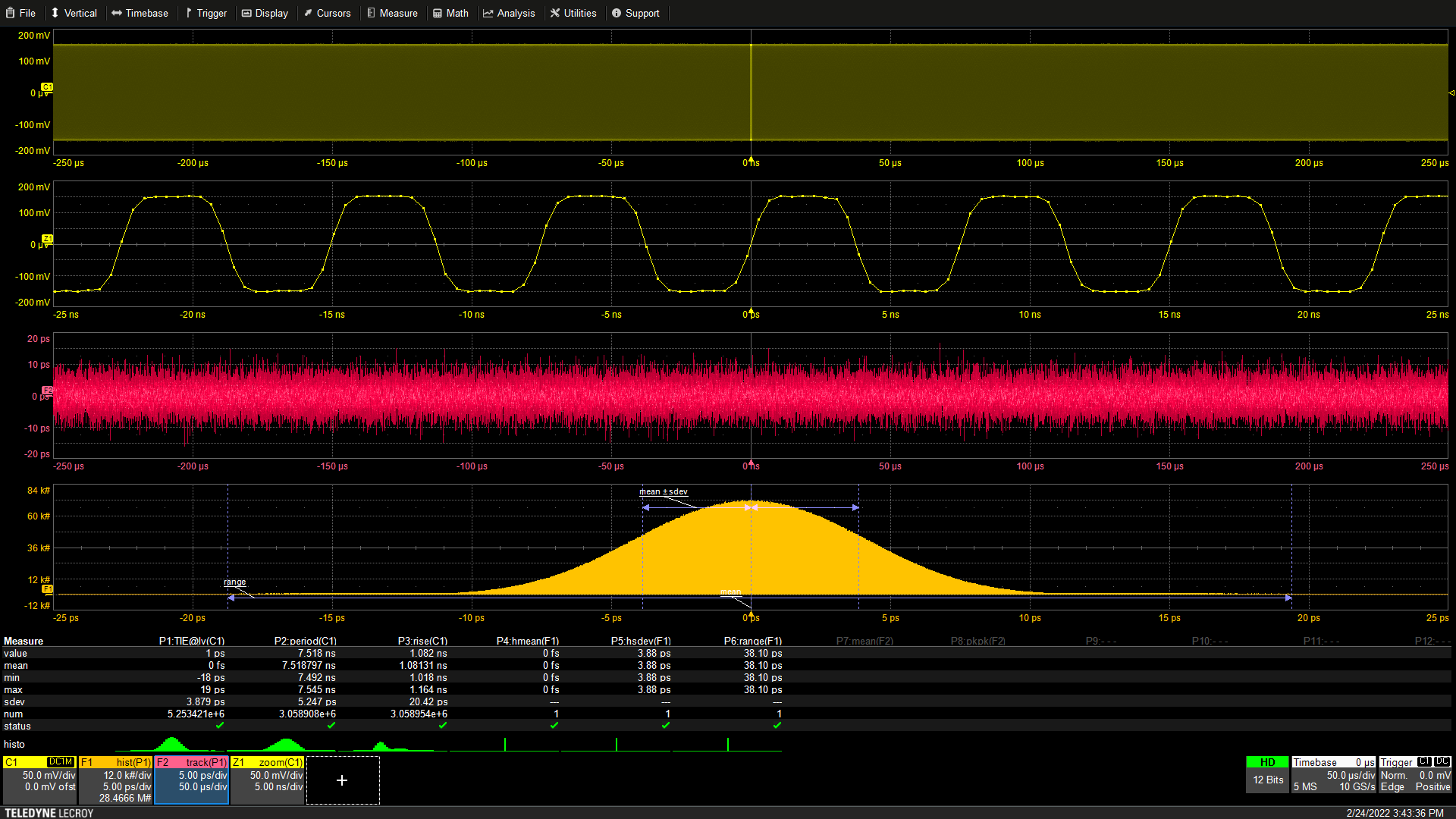

3. 实时功耗波形捕获

借助高采样率电源分析仪(如Keysight N6705C),可捕获微秒级功耗波动,识别异常功耗事件(如未预期的唤醒或泄漏路径)。

能效验证的关键技术

能效基准测试框架

| 测试维度 | 常用基准工具 | 适用场景 |

|---|---|---|

| 通用计算能效 | CoreMark, EEMBC | MCU、嵌入式处理器 |

| AI推理能效 | MLPerf Tiny | 边缘AI芯片 |

| 通信能效 | 3GPP功耗测试规范 | 5G/蓝牙/Wi-Fi SoC |

| 电池续航模拟 | 用户场景建模 + 功耗积分 | 智能手表、TWS耳机等 |

温度与电压扫描(Corner Testing)

低功耗芯片需在 PVT(工艺-电压-温度) 极端条件下验证能效稳定性:

- 电压扫描:从标称电压下探至亚阈值区域(如0.6V)

- 温度梯度:-40°C ~ 125°C 多点测试

- 工艺角:FF(快快)、SS(慢慢)等Corner仿真+实测比对

常见测试陷阱与规避建议

- ❌ 仅依赖仿真数据:仿真无法完全反映物理漏电与封装寄生效应

- ❌ 忽略电源完整性:电源噪声会显著影响低功耗模式稳定性

- ✅ 建议:采用“仿真+实测+场景回放”三位一体验证策略

未来趋势:从“测功耗”到“优能效”

随着Chiplet、3D封装与近阈值计算(Near-Threshold Computing)的发展,低功耗测试正向 系统级能效验证 演进。测试不再局限于芯片本身,而是涵盖电源管理IC(PMIC)、固件调度策略甚至软件算法对整体能效的影响。

总结:精准测试,是能效优化的起点

低功耗芯片的竞争力不仅在于设计,更在于可验证、可复现的能效表现。通过科学的测试方法、严谨的验证流程和多维数据交叉分析,企业才能真正实现“低功耗”承诺,赢得市场与认证的双重认可。在绿色电子浪潮中,能效测试已从辅助环节升级为核心技术能力。

深圳晟安检测专注于半导体芯片的全生命周期可靠性与能效验证服务,提供符合JEDEC、AEC-Q、ISO等国际标准的低功耗测试解决方案,覆盖静态/动态功耗分析、能效基准测试、PVT Corner验证等关键环节,助力客户加速产品上市并确保能效合规。