在早期的低速电路设计中,电源设计只需关注“电压够不够,电流大不大”。但在如今动辄GHz的高速数字系统中,工程师们发现一个奇怪的现象:信号走线明明设计得很完美,阻抗匹配也做了,但眼图依然闭合,误码率居高不下。这时候,问题往往不出在信号线上,而是在电源层——这就是功率完整性(PI)对信号完整性(SI)的“降维打击”。

PI是如何毁掉SI的?

信号完整性和功率完整性并不是孤立的。当芯片内部大量的晶体管同时翻转(0变1或1变0)时,会瞬间抽取巨大的电流。如果电源分配网络(PDN)的阻抗不够低,就会产生电压跌落或波动。

1. 同步开关噪声 (SSN)

地弹(Ground Bounce)和电源塌陷(Rail Collapse)会直接叠加到信号上,导致信号电平波动,严重时造成逻辑误判。

2. 抖动 (Jitter) 的引入

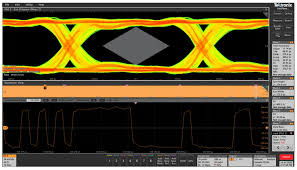

电源噪声会通过芯片内部的驱动器耦合到输出信号上,表现为时序上的抖动(PSIJ – Power Supply Induced Jitter)。这对于对时钟精度要求极高的高速链路是致命的。

3. 回流路径的破坏

高速信号的回流路径通常是参考电源平面或地平面。如果电源平面充满了高频噪声,信号的回流也会受到干扰,导致EMI辐射增加。

SI/PI协同测试的必要性

传统的测试方法往往将两者割裂:电源工程师测纹波,信号工程师测眼图。现在的趋势是必须结合分析:

- PDN阻抗测试: 使用矢量网络分析仪(VNA)测量电源地之间的阻抗,确保在全频段内低于目标阻抗。

- 噪声关联分析: 在示波器上同时监测电源纹波和信号抖动,观察两者的相关性,确认信号恶化是否由电源引起。

总结

如果不解决PI问题,SI优化就像是在沙滩上盖楼。只有构建了低阻抗、低噪声的电源高速公路,高速信号这辆跑车才能跑得快、跑得稳。SI/PI协同设计与测试,已成为高端芯片及PCB设计的必修课。

深圳德恺具备行业领先的SI/PI协同测试能力。我们配备了高性能VNA及实时示波器,能够为您提供从PDN目标阻抗仿真验证、电源纹波频谱分析到SSN噪声排查的全套解决方案,帮助您解决最棘手的高速电路干扰问题。