在现代高速电子系统设计中,信号完整性是决定产品性能与可靠性的基石。随着数据传输速率不断提升,信号在传输路径上受到的损耗、反射、串扰等问题日益突出,这使得系统性的测试与验证不再是设计完成后的补充环节,而是贯穿产品开发周期的核心活动。明确测试的最佳阶段与时机,能够高效定位问题、降低返工成本,并最终确保产品一次成功。

信号完整性测试的核心阶段

根据行业实践与最新技术资料,信号完整性测试并非单一时间点的任务,而是一个与设计流程深度耦合的持续过程。其最佳介入点主要集中在两个关键阶段。

1. 设计仿真与预布线阶段

在硬件物理实现之前,利用仿真工具进行预布线分析是避免后期重大设计缺陷的第一道防线。此阶段的目标是在图纸上解决潜在的信号完整性问题。

- 预期测量与建模:对通道、连接器、电缆、背板或PCB的预期性能进行建模和仿真。

- 规则定义:确定阻抗控制、串扰限值等关键设计规则。

- 可行性验证:通过仿真验证设计概念的可行性,为后续硬件测试提供参考基准。

2. 硬件原型验证阶段

当设计从仿真阶段进展到实体硬件环节时,理论模型需要接受实践的检验。这是测试活动中最具体、最直接的阶段。

此时,矢量网络分析仪成为测试高速数字互连性能的关键仪器。VNA通过在频域进行测量,能够精确表征互连通道的S参数(如插入损耗、回波损耗),从而评估其带宽和阻抗一致性。测试应在首批硬件原型可用后立即展开,并与仿真结果进行比对,以确认设计是否达标或发现未预料到的寄生效应。

确保信号完整性的系统性步骤

成功的信号完整性管理遵循一个结构化的流程。以下结合行业经验,概述10个关键步骤:

- 设计前准备:明确系统规格、标准与目标。

- 电路板层叠设计:规划叠层结构以满足阻抗控制和电源完整性需求。

- 串扰与阻抗控制:制定布线规则,控制特征阻抗并最小化串扰。

- 标识关键高速节点:如时钟、高速串行总线等,进行重点防护。

- 技术选型:选择合适的元器件、连接器和板材。

- 预布线阶段仿真:实施前述的仿真验证。

- 布线后信号完整性仿真:基于实际布局布线进行更精确的仿真。

- 后制造阶段测试:对生产出的PCB进行实体验证,即硬件原型测试。

- 测试数据分析与调试:对比仿真与实测数据,定位并解决问题。

- 迭代优化:根据测试结果反馈至设计,完成设计闭环。

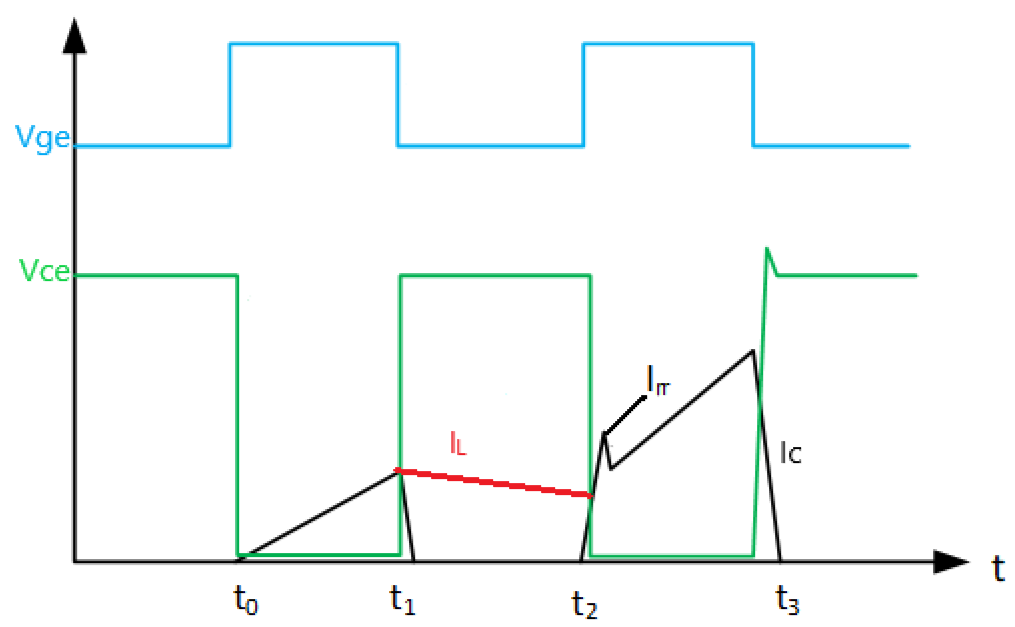

时域与频域:不可或缺的两种视角

全面的信号完整性测试需要结合时域和频域两种分析方法,它们互为补充,揭示了信号不同侧面的特性。

| 测试维度 | 主要仪器 | 评估内容 | 关键指标 |

|---|---|---|---|

| 频域测试 | 矢量网络分析仪 | 通道的传输特性、阻抗匹配 | S参数(插入损耗、回波损耗) |

| 时域测试 | 高速示波器 | 信号波形质量、时序关系 | 眼图、上升时间、抖动 |

例如,在时域分析中,眼图测试是评估高速串行信号质量的通用方法。通过叠加数千个(例如约3000个)信号周期,可以直观观察时序抖动和噪声容限。现代仪器配合分析软件,能对眼图进行深度解析,如精确统计在模板内的采样点违规情况,为性能判定提供量化依据。

结论:将测试融入开发血脉

信号完整性测试的最佳实践是“左移”——尽可能在开发早期介入,并通过仿真与实测的反复迭代,将问题扼杀在萌芽状态。其最佳时机清晰地位于设计完成前的仿真阶段与硬件原型出炉后的验证阶段之间。把握这两个节点,并系统性地执行从设计前准备到后制造测试的完整步骤,同时融合时域与频域的测试手段,是保障高速电子产品一次成功、赢得市场的关键。

深圳德垲:您的专业信号完整性测试伙伴

作为专业的第三方半导体检测与车规认证服务机构,深圳德垲深刻理解信号完整性对产品可靠性的决定性影响。我们拥有先进的矢量网络分析仪、高速示波器等测试平台,以及经验丰富的技术团队,能够为客户提供从设计仿真咨询、原型板测试到认证前全项目验证的一站式服务。尤其在汽车电子等高可靠性要求领域,我们助力客户精准把握测试时机,严格遵循相关流程,确保产品信号性能满足严苛的行业标准与车规要求,为产品的成功上市保驾护航。