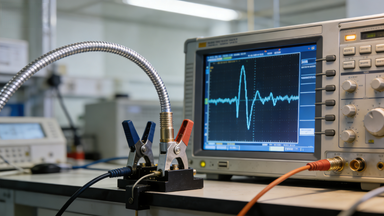

信号完整性测试的最佳阶段与时机

本文探讨信号完整性测试在硬件开发仿真与硬件环节间的关键时机,解析VNA测试方法及结合时域频域的10个步骤,确保高速互连设计可靠。

本文探讨信号完整性测试在硬件开发仿真与硬件环节间的关键时机,解析VNA测试方法及结合时域频域的10个步骤,确保高速互连设计可靠。

信号完整性不佳将直接导致车规产品出现数据错误、间歇性系统故障及硬件失效,增加设计与维护风险。本文深入解析其影响及检测认证的重要性。

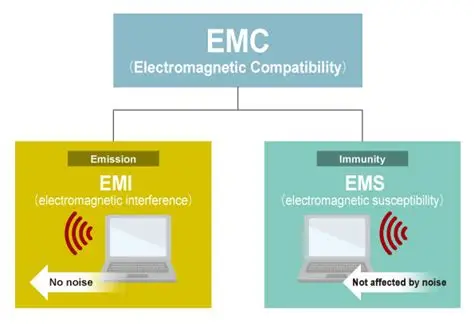

SI关注波形质量,EMC关注对外干扰,两者看似独立实则紧密相关。本文深度解析信号完整性问题(如反射、振铃)如何导致EMI辐射超标,探讨SI/EMC协同整改的最佳实践。

串扰是高速电路设计的头号杀手。本文详解近端串扰(NEXT)与远端串扰(FEXT)的产生机理与测试方法,揭示S参数分析技巧与减小串扰的PCB设计策略,助您优化信号完整性。

专业FAKRA、HSD、USB连接器信号完整性测试,覆盖汽车、通信等多领域,CNAS认可,40+主机厂信赖。

注意:每日仅限20个名额

广州分公司

地址:广州市黄埔区云埔街源祥路96号弘大商贸创意园5号楼605房

深圳分公司

地址:深圳市坪山区碧岭街道碧岭社区坪山金碧路543号忠诚科技大厦801B

上海分公司

地址:上海市奉贤区星火开发区莲塘路251号8幢

芜湖分公司

地址:安徽省芜湖市镜湖区范罗山街道黄山中路金鼎大厦1411