在摩尔定律逼近物理极限的今天,芯片制程不断微缩、结构日益复杂,对集成电路(IC)检测技术提出了前所未有的挑战。从5nm到3nm甚至更先进节点,制造缺陷可能仅几个原子大小,传统检测手段已难以满足高良率、高可靠性的产业需求。与此同时,先进封装(如Chiplet、3D堆叠)的兴起,也让检测维度从平面走向立体。本文将系统梳理当前集成电路检测领域的关键突破与发展趋势,为行业提供前瞻性洞察。

检测精度迈入“亚纳米”时代

随着EUV光刻技术的普及,芯片缺陷尺寸已缩小至1–2纳米级别。为匹配这一精度,检测设备也同步升级:

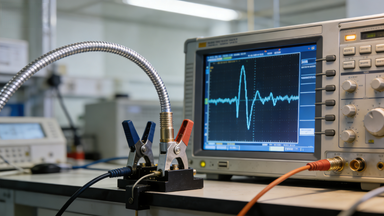

- 高分辨率电子束检测(e-beam inspection):可识别小于1nm的金属桥接、短路等缺陷。

- 原子力显微镜(AFM)集成方案:用于晶圆表面形貌与电性同步分析,提升缺陷定位效率。

- 光学检测+AI算法融合:通过深度学习模型从海量图像中筛选异常,大幅降低误报率。

AI驱动的智能缺陷识别

从“看得见”到“看得懂”

传统检测依赖人工设定阈值,效率低且易漏检。如今,AI正重构检测逻辑:

- 自监督学习模型 可在无标注数据下自动识别异常模式。

- 跨工艺节点迁移学习 允许模型在新产线快速部署,缩短调试周期。

- 实时反馈闭环:检测结果直接联动工艺控制系统,实现“检测–修正”一体化。

举例:台积电在3nm产线中部署AI检测系统后,缺陷检出率提升35%,误判率下降50%。

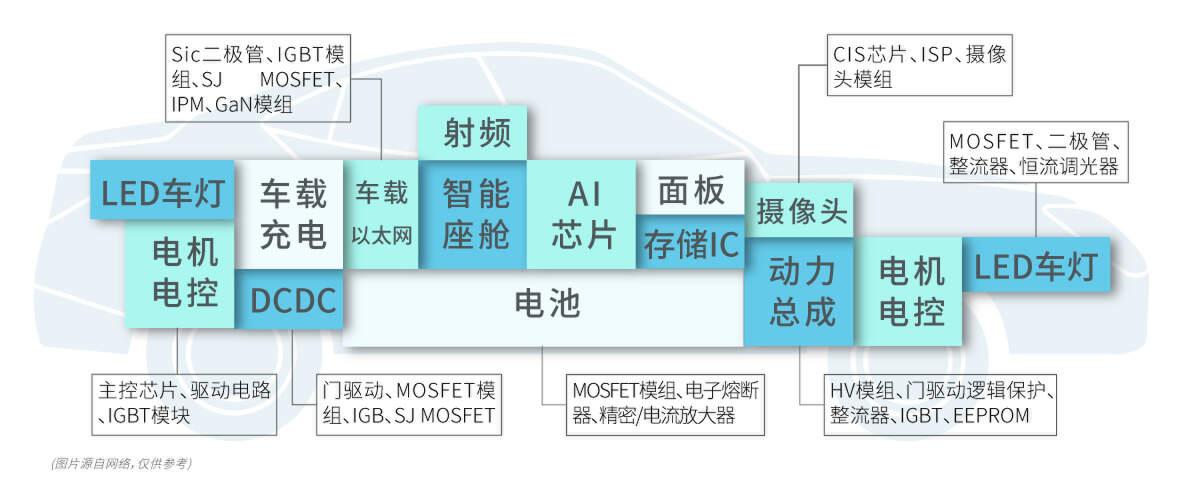

先进封装带来的检测新范式

3D结构,多维挑战

Chiplet、FOWLP、TSV等先进封装技术,使芯片从“平面”走向“立体”,检测复杂度指数级上升:

| 封装类型 | 检测难点 | 主流解决方案 |

|---|---|---|

| 2.5D/3D IC | 硅通孔(TSV)对准与空洞 | X射线断层扫描(CT) |

| Fan-Out | 重布线层(RDL)微裂纹 | 红外热成像+机器视觉 |

| Chiplet集成 | 异质芯片间互连可靠性 | 电性测试+声学显微(SAM) |

无损检测技术加速演进

为避免破坏昂贵样品,无损检测(NDT)成为主流方向:

- 高能X射线成像:穿透多层结构,精准识别内部空洞、分层。

- 太赫兹检测:对非金属材料(如封装树脂)缺陷敏感,适用于Fan-Out封装。

- 激光超声技术:可探测微米级界面脱粘,适用于晶圆级封装(WLP)。

检测效率与成本的平衡术

先进节点检测成本已占制造总成本15%以上。行业正通过以下方式优化ROI:

- 多模态融合检测:一次扫描同步获取形貌、电性、材料信息。

- 边缘计算部署:在设备端完成初步分析,减少数据传输延迟。

- 虚拟检测(Virtual Inspection):基于工艺数据预测缺陷位置,仅对高风险区域实测。

总结

集成电路检测已从单一的“缺陷发现”工具,演变为支撑先进制程与封装良率的核心引擎。AI、多物理场融合、无损成像等技术的协同创新,正在重塑检测的精度、速度与维度。未来,随着GAA晶体管、CFET等新结构落地,检测技术将持续向更高分辨率、更强智能、更深集成方向演进,成为半导体产业突破“后摩尔时代”瓶颈的关键支点。

深圳晟安检测专注于半导体领域高精度检测服务,提供涵盖晶圆缺陷分析、先进封装可靠性验证、失效分析(FA)及材料表征的一站式解决方案。依托先进的电子束检测系统、3D X射线断层扫描平台及AI驱动的数据分析能力,我们助力客户提升产品良率、加速研发迭代。如需了解集成电路专业检测服务,请联系晟安检测技术团队。